TWI结构

一、数据协议:

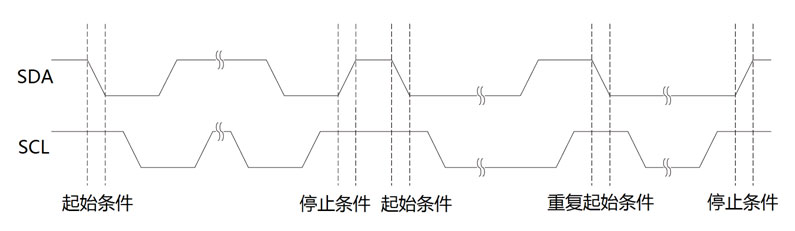

TWI总线协议规定总线上在进行数据位传输时需要与时钟脉冲同步,在数据传送过程中,当时钟线为高电平时,数据线上的电平必须保持稳定。(如果在时钟线为高电平时,数据线电平变化视作协议开始或停止),TWI总线数据传输如下图:

TWI总线上的一个数据帧由9个位构成,包括8个数据位和一个应答位,数据的高位在前,低位在后,总线上发送数据的一方称为发送器,接收数据的一方称为接收器。当8位的数据发送完毕后,接收器在第9个时钟到来之前拉低SDA线以产生应答信号(ACK),当接收器由于某种原因不能继续接收数据时,可以在第9个时钟到来时不拉低SDA线,即产生一个非应答信号(NACK),以此通知发送器不要继续发送数据。TWI总线上数据帧格式如下图:

起始条件和停止条件,TWI总线协议规定在时钟线SCL为高电平时,数据线SDA从高电平向低电平的跳变被定义为起始条件,反之则定义为停止条件。

TWI总线上数据传输都是以主机产生的起始条件(START)开始,以主机产生的停止条件(STOP)终止,在起始条件之后TWI总线被认为进入了忙状态。有时为了需要,也可以在一个起始条件后,再次产生一个起始条件,我们称之为重复起始条件,同理也有重复停止条件,如下图:

地址帧格式:TWI总线规定一个地址帧由9位构成,即7位的从器件地址、1位的读定控制位和1位应答位。主机先将7位的器件地址按高位在前、低位在后的顺序依次放置在总线上,之后主机发送一个读定控制位,读写控制位为1时,表示接下业主机要对主机进行读操作,而当读写控制位为0时,表示接下来主机将要对从机进行写操作。从机在检测到自身被寻址后,在第9个时钟周期开始前将SDA线拉低作出应答(ACK),如下图:

二相关寄存器:

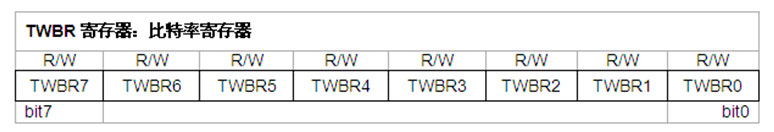

1、TWBR寄存器。

该寄存器是TWI模块的比特率寄存器,用于保存设定的分频比,以此来控制TWI模块的比特率。比特率发生器只是一个分频器,它将系统时钟分频后在SCL线上产生时钟信号。

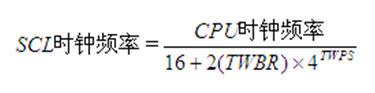

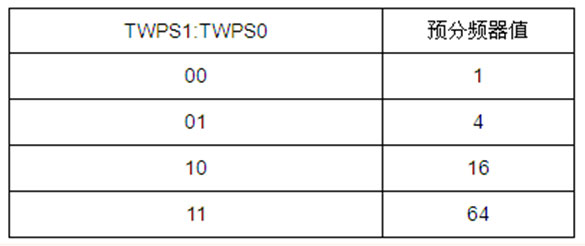

SCL线上的时钟频率不仅与比特率寄存器TWBR的值有关,还与状态寄存器TWSR的TWPS1:TWPS0位所设定的预分频系数有关,具有计算公式如下:

注:在主机模式下,TWBR的值不能小于10,否则会从SDA和SCL线上输出错误的信号。

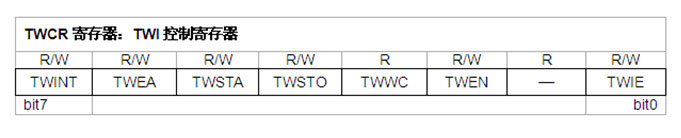

2、TWCR寄存器。

Bit7 TWINT:TWI中断标志位。该位置1表示产生了TWI相关事件的中断,当中断产生时,SCL线将保持低电平,时钟暂停。如果此时SREG的I位和TWCR寄存器的TWIE位均置1,则表示该中断得到允许,单片机会跳到TWI中断向量地址处开始执行中断服务程序。

在执行中断服务程序后,TWINT位不能硬件清0,需要通过软件向该位写1才能清0此位。TWINT位也被用于启动TWI模块的运行,当TWINT位清0时,TWI模块会立即开始下一步的工作,因此在清零TWINT位之前要先完成对地址寄存器TWAR,状态寄存器TWSR,以及数据寄存器TWDR的数据写入。

Bit6 TWEA:应答信号使能位。该位置1时,出现如下条件时总线上产生应答信号:

A 单片机的从地址和主机发出的地址相符。

B 广播呼叫功能得到允许后,单扯机接收到广播呼叫。

C 在主机或从机模式下接收到一个字节的数据。

Bit5 TWSTA:起始信号使能位。该位置1时,TWI模块会硬件判断总线状态,一旦总线空闲,就会在总线上产生一个起始条件。如果总线忙,TWI模块就会持续监视总线,直到检测到一个停止信号后,再产生起始信号,以表明已需要成为主机。

Bit4:TWSTO:停止信号使能位。在主机模式下,该位置1时,TWI模块会在总线上产生一个停止条件。停止条件产生后,TWSTO位自动硬件清0.在从机模式下,将该位置1会使TWI接口从错误状态恢复到未被寻址状态,但总线上不会产生停止信号。

Bit3:TWWC:写冲突标志位。当TWINT清0时,将数据定入TWDR将会使用TWWC位置1,表示产生了写冲突,只有当TWINT位置1时,TWI模块的移位寄存器为空闲状态,此时才能软件写入TWDR寄存器。

Bit2:TWEN:TWI模块使能位。该位置1时激活TWI端口,并将引脚配置成SCL和SDA状态。

Bit1:未定义

Bit0:TWIE:TWI模块的中断允许位。该位置1时使能TWI中断,如果TWINT位置1且全局中断得到允许,单片机则会执行中断服务程序。

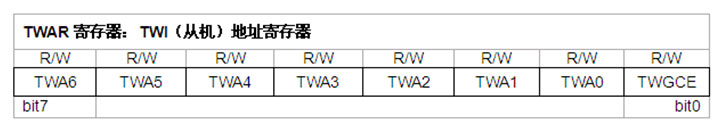

3、TWAR寄存器

Bit7-1 TWA6-TWA0:TWI从机地址。

Bit0:TWGCE:使能TWI广播识别。该位置1后MCU可以识别到TWI总线广播地址的呼叫。

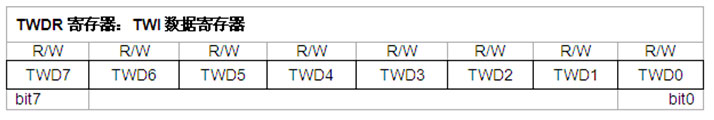

4、TWDR寄存器

该寄存器是TWI模块的数据寄存器,在发送模式下,TWDR存放待发送数据,在接收模式下,TWDR保存已经接收到的数据。当TWI中断标志位TWINT置1后,TWDR寄存器中的数据才是稳定的,所以对TWDR寄存器的读写需要在TWINT置1后进行。

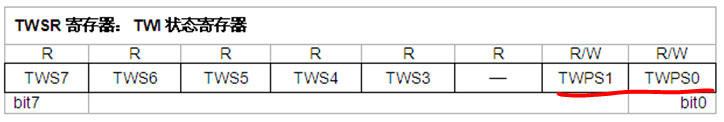

5、TWSR寄存器

Bit7-3 TWS7-TWS3:TWI模块的状态位,用于反映TWI逻辑和总线的状态,具体见下表。

Bit2:未使用。

Bit1-0 TWPS1-TWPS0:TWI模块预分频选择位,用于控制时钟线上比特率值,具体见下表。

评论列表

我要评论